Product Specification

Page 4

...; Core™ Processor i3-2100 Series 17 Intel® Turbo Boost Technology 17 3.2 Memory Subsystem 17 3.2.1 Memory Supported 18 3.2.2 Post Error Codes 18 3.2.3 Memory Map and Population Rules 19 3.2.4 Publishing System Memory 21 3.2.5 3.3 Memory RAS Support 21 Intel® Chipset PCH 21 3.4 I /O Layout 14 3. Overview ...2 2.1 Intel® Server Board S1200BT Feature Set 2 2.2 Server Board Layout 4 2.2.1 2.2.2 Server Board Connector and...

...; Core™ Processor i3-2100 Series 17 Intel® Turbo Boost Technology 17 3.2 Memory Subsystem 17 3.2.1 Memory Supported 18 3.2.2 Post Error Codes 18 3.2.3 Memory Map and Population Rules 19 3.2.4 Publishing System Memory 21 3.2.5 3.3 Memory RAS Support 21 Intel® Chipset PCH 21 3.4 I /O Layout 14 3. Overview ...2 2.1 Intel® Server Board S1200BT Feature Set 2 2.2 Server Board Layout 4 2.2.1 2.2.2 Server Board Connector and...

Product Specification

Page 5

... Management Interface (DCMI 41 4.2.7 Local Directory Authentication Protocol (LDAP 41 4.3 Thermal Control 41 4.3.1 Memory Thermal Throttling 41 4.3.2 4.4 Fan Speed Control 42 Intel® Intelligent Power Node Manager 42 4.4.1 Overview ...42 4.4.2 Features...43 4.4.3 Role of Contents ... Keyboard and Mouse Support 28 3.6.6 Wake-up Control 28 3.7 3.7.1 3.7.2 Video Support ...28 Intel® Server Board S1200BTL 28 Video for Intel® Server Board S1200BTS 29 3.8 Network Interface Controller (NIC 29 3.8.1 Gigabit Ethernet Controller 82574L 29 3.8.2 Gigabit Ethernet...

... Management Interface (DCMI 41 4.2.7 Local Directory Authentication Protocol (LDAP 41 4.3 Thermal Control 41 4.3.1 Memory Thermal Throttling 41 4.3.2 4.4 Fan Speed Control 42 Intel® Intelligent Power Node Manager 42 4.4.1 Overview ...42 4.4.2 Features...43 4.4.3 Role of Contents ... Keyboard and Mouse Support 28 3.6.6 Wake-up Control 28 3.7 3.7.1 3.7.2 Video Support ...28 Intel® Server Board S1200BTL 28 Video for Intel® Server Board S1200BTS 29 3.8 Network Interface Controller (NIC 29 3.8.1 Gigabit Ethernet Controller 82574L 29 3.8.2 Gigabit Ethernet...

Product Specification

Page 8

... Bus (SMBUS) Block Diagram 32 Figure 15. Advanced Screen...59 Figure 17. Console Redirection Screen 77 Figure 28. Intel® Server Board S1200BT Rear I/O Layout 14 Figure 11. Intel® Server Board S1200BTL Functional Block Diagram 15 Figure 12. Memory Configuration Screen 68 Figure 19. PCI Configuration Screen 74 Figure 23. Server Management Screen...

... Bus (SMBUS) Block Diagram 32 Figure 15. Advanced Screen...59 Figure 17. Console Redirection Screen 77 Figure 28. Intel® Server Board S1200BT Rear I/O Layout 14 Figure 11. Intel® Server Board S1200BTL Functional Block Diagram 15 Figure 12. Memory Configuration Screen 68 Figure 19. PCI Configuration Screen 74 Figure 23. Server Management Screen...

Product Specification

Page 10

...Pin-out (J1J2 93 Table 25. SGPIO Header Pin-out (J1J3 on S1200BTL and J2J2 on S1200BTS) ...93 Table 27. List of Tables Intel®Server Board S1200BT TPS List of Tables Table 1. UDIMM memory configuration rule 20 Table 6. NM Features ...43 Table 13. Major Board Components 7 Table 4. ...; Server Board S1200BT Feature Set 2 Table 2. UDIMM Maximum configuration 20 Table 7. Intel® RMM4 lite Connector Pin-out (J4B1 92 Table 22. BIOS Setup: Keyboard Command Bar 52 Table 16. RJ-45 10/100/1000 NIC Connector Pin-out 96 Table 30. Memory Configuration Table 20 Table 5....

...Pin-out (J1J2 93 Table 25. SGPIO Header Pin-out (J1J3 on S1200BTL and J2J2 on S1200BTS) ...93 Table 27. List of Tables Intel®Server Board S1200BT TPS List of Tables Table 1. UDIMM memory configuration rule 20 Table 6. NM Features ...43 Table 13. Major Board Components 7 Table 4. ...; Server Board S1200BT Feature Set 2 Table 2. UDIMM Maximum configuration 20 Table 7. Intel® RMM4 lite Connector Pin-out (J4B1 92 Table 22. BIOS Setup: Keyboard Command Bar 52 Table 16. RJ-45 10/100/1000 NIC Connector Pin-out 96 Table 30. Memory Configuration Table 20 Table 5....

Product Specification

Page 14

... with support for 1066/1333 MHz ECC Unbuffered (UDIMM) DDR3. It has two board SKUs, namely S1200BTL and S1200BTS. 2.1 Intel® Server Board S1200BT Feature Set Feature Processor Memory Chipset I/O Table 1. Description of board Internal connections: Two USB 2x5 pin headers, each supporting two USB 2.0 ports One 2x5 Serial Port B headers ...

... with support for 1066/1333 MHz ECC Unbuffered (UDIMM) DDR3. It has two board SKUs, namely S1200BTL and S1200BTS. 2.1 Intel® Server Board S1200BT Feature Set Feature Processor Memory Chipset I/O Table 1. Description of board Internal connections: Two USB 2x5 pin headers, each supporting two USB 2.0 ports One 2x5 Serial Port B headers ...

Product Specification

Page 15

...SATA II connectors with SW RAID 0, 1, 5 and 10. One Gigabit Ethernet device 82574L connect to PCH through PCI-E x1 interface - Intel®Server Board S1200BT TPS Overview Feature Add-in PCI Card, PCI Express* Card System Fan Support Video Onboard Hard Drive RAID Support LAN Server Management Security ...pin fan headers supporting four system fans and one processor Onboard ServerEngines* LLC Pilot III BMC Controller External 32MB (or above) DDR3 800MHz memory Support for six Serial ATA II hard drives through six onboard SATA II connectors with SW RAID 0, 1, 5, and 10 Up to four SAS...

...SATA II connectors with SW RAID 0, 1, 5 and 10. One Gigabit Ethernet device 82574L connect to PCH through PCI-E x1 interface - Intel®Server Board S1200BT TPS Overview Feature Add-in PCI Card, PCI Express* Card System Fan Support Video Onboard Hard Drive RAID Support LAN Server Management Security ...pin fan headers supporting four system fans and one processor Onboard ServerEngines* LLC Pilot III BMC Controller External 32MB (or above) DDR3 800MHz memory Support for six Serial ATA II hard drives through six onboard SATA II connectors with SW RAID 0, 1, 5, and 10 Up to four SAS...

Product Specification

Page 29

...its package. Only ECC memory is enabled. 3.2 Memory Subsystem The Intel® Xeon® Processor E3-1200 series or Intel® Core™ Processor i3-2100 has an Integrated Memory Controller (IMC) in the Intel® Xeon® Processor E3-1200 Series. Intel® Turbo Boost ...; Turbo Boost availability is featured on active cores. Revision 1.0 17 Intel order number G13326-003 Intel®Server Board S1200BT TPS Functional Architecture The server board does not support previous generations of the Intel® Core™ Processor i3 Series. Note: The workstation processor ...

...its package. Only ECC memory is enabled. 3.2 Memory Subsystem The Intel® Xeon® Processor E3-1200 series or Intel® Core™ Processor i3-2100 has an Integrated Memory Controller (IMC) in the Intel® Xeon® Processor E3-1200 Series. Intel® Turbo Boost ...; Turbo Boost availability is featured on active cores. Revision 1.0 17 Intel order number G13326-003 Intel®Server Board S1200BT TPS Functional Architecture The server board does not support previous generations of the Intel® Core™ Processor i3 Series. Note: The workstation processor ...

Product Specification

Page 30

Functional Architecture Intel®Server Board S1200BT TPS The memory channels are named as ―Channel A‖ and ―Channel B‖. The memory slots are installed: o Channel A, Slot1 is ―DIMM_A1‖. In late POST, this section, the ... Diagnostic LED code 0xE8 and halts the system. 18 Revision 1.0 Intel order number G13326-003 No Usable Memory Error: If no usable memory is ―DIMM_B2‖. 3.2.1 Memory Supported The Intel® Server Board S1200BT family supports various DDR3 DIMM modules of support are subject to reflect...

Functional Architecture Intel®Server Board S1200BT TPS The memory channels are named as ―Channel A‖ and ―Channel B‖. The memory slots are installed: o Channel A, Slot1 is ―DIMM_A1‖. In late POST, this section, the ... Diagnostic LED code 0xE8 and halts the system. 18 Revision 1.0 Intel order number G13326-003 No Usable Memory Error: If no usable memory is ―DIMM_B2‖. 3.2.1 Memory Supported The Intel® Server Board S1200BT family supports various DDR3 DIMM modules of support are subject to reflect...

Product Specification

Page 31

...by full 64-byte cache lines alternating between channels, i.e. Intel®Server Board S1200BT TPS Functional Architecture This can also occur if all of the memory fails memory testing, then system memory error code 0xE8 (No Usable Memory) as the highest address on the less-populated channel, then... to properly perform the Data/Data Strobe timing training on the Intel® Server Board S1200BT. Otherwise, the system beeps and halts with different numbers of DIMMs installed. Population Error: If the installed memory contains an invalid DIMM configuration on any channel in Dual Channel ...

...by full 64-byte cache lines alternating between channels, i.e. Intel®Server Board S1200BT TPS Functional Architecture This can also occur if all of the memory fails memory testing, then system memory error code 0xE8 (No Usable Memory) as the highest address on the less-populated channel, then... to properly perform the Data/Data Strobe timing training on the Intel® Server Board S1200BT. Otherwise, the system beeps and halts with different numbers of DIMMs installed. Population Error: If the installed memory contains an invalid DIMM configuration on any channel in Dual Channel ...

Product Specification

Page 32

... Ranks per channel Single Rank, Dual Rank Single Rank, Dual Rank To get the maximum memory size on UDIMM, you get the detailed information from following table: Table 6. Functional Architecture Intel®Server Board S1200BT TPS The maximum memory bandwidth is 10.6 GB/s in Single-Channel mode or 21 GB/s in Dual-Channel...

... Ranks per channel Single Rank, Dual Rank Single Rank, Dual Rank To get the maximum memory size on UDIMM, you get the detailed information from following table: Table 6. Functional Architecture Intel®Server Board S1200BT TPS The maximum memory bandwidth is 10.6 GB/s in Single-Channel mode or 21 GB/s in Dual-Channel...

Product Specification

Page 33

...the 10th CE occurs, a single Correctable Error event is logged. 3.3 Intel® Chipset PCH The Intel® C200Series Chipset is Error Correction Code (ECC). Intel®Server Board S1200BT TPS Functional Architecture Max Memory Possible 1Gb DRAM Technology (4x 2GB DIMMs) 2Gb DRAM Technology (4x ... ECC Error event is a single processor/IMC, with no interleaving. 3.2.5 Memory RAS Support For Intel® Server Board S1200BT, the form of DIMMs installed. In each 64 bits of memory is crossed. Correctable Errors are just silently recorded until the tolerance threshold is...

...the 10th CE occurs, a single Correctable Error event is logged. 3.3 Intel® Chipset PCH The Intel® C200Series Chipset is Error Correction Code (ECC). Intel®Server Board S1200BT TPS Functional Architecture Max Memory Possible 1Gb DRAM Technology (4x 2GB DIMMs) 2Gb DRAM Technology (4x ... ECC Error event is a single processor/IMC, with no interleaving. 3.2.5 Memory RAS Support For Intel® Server Board S1200BT, the form of DIMMs installed. In each 64 bits of memory is crossed. Correctable Errors are just silently recorded until the tolerance threshold is...

Product Specification

Page 35

... and a user interface for configuration and management of the RAID capability of PCH. 3.4.4 Low Pin Count (LPC) Interface The Intel® C200 Series chipset implements an LPC Interface as no master/slave designation for details on self test (POST), the BIOS ...memory space. All ports are located on two disks. speed, and low-speed capable. Four external connectors are high-speed, full- The Intel® C200 Series chipset PCH provides hardware support for AHCI, a standardized programming interface for up to ten USB 2.0 ports. Intel®Server Board S1200BT...

... and a user interface for configuration and management of the RAID capability of PCH. 3.4.4 Low Pin Count (LPC) Interface The Intel® C200 Series chipset implements an LPC Interface as no master/slave designation for details on self test (POST), the BIOS ...memory space. All ports are located on two disks. speed, and low-speed capable. Four external connectors are high-speed, full- The Intel® C200 Series chipset PCH provides hardware support for AHCI, a standardized programming interface for up to ten USB 2.0 ports. Intel®Server Board S1200BT...

Product Specification

Page 36

... and configures the root hub ports and searches for a keyboard and/or a mouse on ServerEngines* Pilot III, but Intel® Server Board S1200BTS does not have the integrated baseboard management control. The following integrated subsystems and features. USB devices are scanned to Digital...BMC management hardware features used by BIOS. Four modules are initialized by the BMC: 400MHz 32-bit ARM9 processor with memory management unit (MMU) Two independent10/100/1000 Ethernet Controllers with RMII (Reduced Media Independent Interface)/RGMII(Reduced Gigabit Media-...

... and configures the root hub ports and searches for a keyboard and/or a mouse on ServerEngines* Pilot III, but Intel® Server Board S1200BTS does not have the integrated baseboard management control. The following integrated subsystems and features. USB devices are scanned to Digital...BMC management hardware features used by BIOS. Four modules are initialized by the BMC: 400MHz 32-bit ARM9 processor with memory management unit (MMU) Two independent10/100/1000 Ethernet Controllers with RMII (Reduced Media Independent Interface)/RGMII(Reduced Gigabit Media-...

Product Specification

Page 37

Intel®Server Board S1200BT TPS Functional Architecture JTAG Master Eight I2C interfaces with programmable blink rate controls on GPIOs Port 80h snooping capability ... Three UARTs Platform Environmental Control Interface (PECI) Six general-purpose timers Interrupt controller Multiple SPI flash interfaces NAND/Memory interface Sixteen mailbox registers for communication between the Integrated BMC and host LPC ROM interface Integrated BMC watchdog timer capability SD...

Intel®Server Board S1200BT TPS Functional Architecture JTAG Master Eight I2C interfaces with programmable blink rate controls on GPIOs Port 80h snooping capability ... Three UARTs Platform Environmental Control Interface (PECI) Six general-purpose timers Interrupt controller Multiple SPI flash interfaces NAND/Memory interface Sixteen mailbox registers for communication between the Integrated BMC and host LPC ROM interface Integrated BMC watchdog timer capability SD...

Product Specification

Page 40

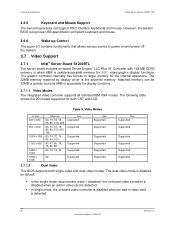

... Dual Video The BIOS supports both CRT and LCD. Functional Architecture Intel®Server Board S1200BT TPS 3.6.5 Keyboard and Mouse Support The server board does not support PS/2 interface keyboards and mouse. Attached memory can be 32MB or greater but only 8MB is detected. 28 ...Revision 1.0 Intel order number G13326-003 However, the system BIOS recognizes USB specification-...

... Dual Video The BIOS supports both CRT and LCD. Functional Architecture Intel®Server Board S1200BT TPS 3.6.5 Keyboard and Mouse Support The server board does not support PS/2 interface keyboards and mouse. Attached memory can be 32MB or greater but only 8MB is detected. 28 ...Revision 1.0 Intel order number G13326-003 However, the system BIOS recognizes USB specification-...

Product Specification

Page 41

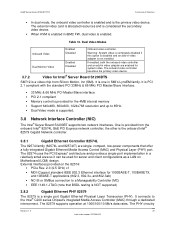

...(82574L and 82574IT) are enabled for the 4MB internal memory Support 640x480, 800x600, 1024x768 resolution and up to 85Hz. Dual Video mode is supported. 3.8 Network Interface Controller (NIC) The Intel® Server Board S1200BT supports two network interfaces, One is one in SMI's ...LAN on the 82574: PCIe Rev. 2.0 (2.5 GHz) x1 MDI (Copper) standard IEEE 802.3 Ethernet interface for Intel® Server Board S1200BTS SM712 is enabled. The 82574 uses the PCI Express* architecture and provides a single-port implementation in iBMC FW, dual video is a ...

...(82574L and 82574IT) are enabled for the 4MB internal memory Support 640x480, 800x600, 1024x768 resolution and up to 85Hz. Dual Video mode is supported. 3.8 Network Interface Controller (NIC) The Intel® Server Board S1200BT supports two network interfaces, One is one in SMI's ...LAN on the 82574: PCIe Rev. 2.0 (2.5 GHz) x1 MDI (Copper) standard IEEE 802.3 Ethernet interface for Intel® Server Board S1200BTS SM712 is enabled. The 82574 uses the PCI Express* architecture and provides a single-port implementation in iBMC FW, dual video is a ...

Product Specification

Page 42

... is reduced to 10 Mb/s (dependent on Intel® Architecture Processors. Functional Architecture Intel®Server Board S1200BT TPS provides a standard IEEE 802.3 Ethernet interface for implementation of Intel® Virtualization Technology with its own subset of host physical memory. The PCIe (main) interface is in independent partitions. Intel® VT-d Technology consists of platforms based...

... is reduced to 10 Mb/s (dependent on Intel® Architecture Processors. Functional Architecture Intel®Server Board S1200BT TPS provides a standard IEEE 802.3 Ethernet interface for implementation of Intel® Virtualization Technology with its own subset of host physical memory. The PCIe (main) interface is in independent partitions. Intel® VT-d Technology consists of platforms based...

Product Specification

Page 53

... BMC firmware and have associated SDRs populated in both hexadecimal and text format. 3. PCI error registers b. MCH registers 4. CPU/memory register data useful for the purpose of DCMI-specific IPMI OEM commands. IPMI users/passwords and sessions are not supported over the any... closed loop throttling (CLTT) of system memory based on availability of data that builds upon a set of required IPMI standard commands by the Integrated BMC for diagnosing the cause of the error conditions. MSR registers c. Intel®Server Board S1200BT TPS Platform Management A list of valid ...

... BMC firmware and have associated SDRs populated in both hexadecimal and text format. 3. PCI error registers b. MCH registers 4. CPU/memory register data useful for the purpose of DCMI-specific IPMI OEM commands. IPMI users/passwords and sessions are not supported over the any... closed loop throttling (CLTT) of system memory based on availability of data that builds upon a set of required IPMI standard commands by the Integrated BMC for diagnosing the cause of the error conditions. MSR registers c. Intel®Server Board S1200BT TPS Platform Management A list of valid ...

Product Specification

Page 54

... enables data center power management by BIOS MRC remain fixed after post. Platform Management Intel®Server Board S1200BT TPS sensors on the installed memory DIMMs. The Integrated Memory Controller (IMC) dynamically changes throttling levels to cap throttling based on memory and system thermal conditions as a closed-loop system with requirements to manage processor power...

... enables data center power management by BIOS MRC remain fixed after post. Platform Management Intel®Server Board S1200BT TPS sensors on the installed memory DIMMs. The Integrated Memory Controller (IMC) dynamically changes throttling levels to cap throttling based on memory and system thermal conditions as a closed-loop system with requirements to manage processor power...

Product Specification

Page 55

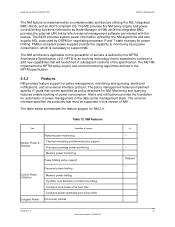

...Platform power monitoring Thermal monitoring and thermal policy support Processor package power monitoring Memory power monitoring Power limiting policy support Control Power Utilization Delegate Power Processor power limiting Memory power limiting Dynamic core allocation (runtime core-idling) Configure core power off...stack. Alerts and notifications provide the foundation for automation of power management in subsequent versions of NM. Intel®Server Board S1200BT TPS Platform Management The NM feature is defined by the NPTM Architecture Specification v2.0. The policy management ...

...Platform power monitoring Thermal monitoring and thermal policy support Processor package power monitoring Memory power monitoring Power limiting policy support Control Power Utilization Delegate Power Processor power limiting Memory power limiting Dynamic core allocation (runtime core-idling) Configure core power off...stack. Alerts and notifications provide the foundation for automation of power management in subsequent versions of NM. Intel®Server Board S1200BT TPS Platform Management The NM feature is defined by the NPTM Architecture Specification v2.0. The policy management ...