Data Sheet

Page 2

... a processor with a processor, chipset, BIOS, operating system, device drivers and applications enabled for conflicts or incompatibilities arising from published specifications. ΔIntel processor numbers are not intended to them. Copyright © 2008, Intel Corporation. See http://developer.intel.com/...PROPERTY RIGHT. Processor numbers differentiate features within each processor family, not across different processor families. The Intel Pentium® dual-core processor E5000 series may contain design defects or errors known as errata which processors support Intel 64 or ...

... a processor with a processor, chipset, BIOS, operating system, device drivers and applications enabled for conflicts or incompatibilities arising from published specifications. ΔIntel processor numbers are not intended to them. Copyright © 2008, Intel Corporation. See http://developer.intel.com/...PROPERTY RIGHT. Processor numbers differentiate features within each processor family, not across different processor families. The Intel Pentium® dual-core processor E5000 series may contain design defects or errors known as errata which processors support Intel 64 or ...

Data Sheet

Page 27

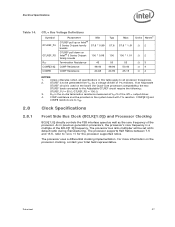

... generated from VTT by a voltage divider of the GTL+ output driver. 4. As in this table apply to the Adjustable GTLREF circuit require the following: GTLREF_PU = 50 Ω, GTLREF_PD = 100 Ω. 3. Unless otherwise noted, all processor frequencies. 2. Datasheet 27 For more information on Intel® 3 Series Chipset family boards Termination Resistance COMP Resistance COMP...

... generated from VTT by a voltage divider of the GTL+ output driver. 4. As in this table apply to the Adjustable GTLREF circuit require the following: GTLREF_PU = 50 Ω, GTLREF_PD = 100 Ω. 3. Unless otherwise noted, all processor frequencies. 2. Datasheet 27 For more information on Intel® 3 Series Chipset family boards Termination Resistance COMP Resistance COMP...

Data Sheet

Page 66

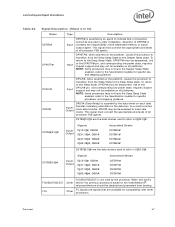

... responsible for that the data bus is inverted. DBR# is asserted by a debug port interposer so that an in processor systems where no connect in the system. The data driver asserts DRDY# to a pair of the D[63:0]# signals.The DBI[3:0]# signals are quad-pumped signals and will, thus..., be driven four times in use. D[63:0]# are activated when the data on all processor FSB agents. 66 Datasheet Input/ Output DBSY...

... responsible for that the data bus is inverted. DBR# is asserted by a debug port interposer so that an in processor systems where no connect in the system. The data driver asserts DRDY# to a pair of the D[63:0]# signals.The DBI[3:0]# signals are quad-pumped signals and will, thus..., be driven four times in use. D[63:0]# are activated when the data on all processor FSB agents. 66 Datasheet Input/ Output DBSY...

Data Sheet

Page 67

...# FC0/BOOTSELECT FCx Other Other FC0/BOOTSELECT is asserted by the data driver on each data transfer, indicating valid data on the Intel NetBurst® microarchitecture should be available on the platform, causes the processor to transition from the Sleep State to the Sleep State, DPSLP# must... connect the appropriate pins/lands of all processor FSB agents. This signal must be ...

...# FC0/BOOTSELECT FCx Other Other FC0/BOOTSELECT is asserted by the data driver on each data transfer, indicating valid data on the Intel NetBurst® microarchitecture should be available on the platform, causes the processor to transition from the Sleep State to the Sleep State, DPSLP# must... connect the appropriate pins/lands of all processor FSB agents. This signal must be ...

Data Sheet

Page 79

...new operating frequency is engaged, the processor will be necessary to transition through multiple VID codes to service any additional hardware, software drivers, or interrupt handling routines. Each step will be latched and kept pending until the processor resumes operation at the lower voltage... reduces the power consumption of the processor. This mechanism provides an efficient means for ...

...new operating frequency is engaged, the processor will be necessary to transition through multiple VID codes to service any additional hardware, software drivers, or interrupt handling routines. Each step will be latched and kept pending until the processor resumes operation at the lower voltage... reduces the power consumption of the processor. This mechanism provides an efficient means for ...