Aspire L350 & Veriton 1000 Service Guide

Page 22

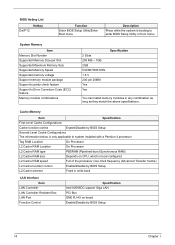

...List Hotkey Del/F12 Function Enter BIOS Setup Utility/Enter Boot menu Description Press while the system is local configured L2 Cache RAM speed Full of the processor core clock frequency (Advanced Transfer Cache) L2 Cache function control Enable/Disable by BIOS Setup L2... The information below is only applicable to system installed with a Pentium 4 processor Tag RAM Location On Processor L2 Cache RAM Location On Processor L2 Cache RAM type PBSRAM (Pipelined-burst Synchronous RAM) L2 Cache RAM size Depends on CPU, which is booting to Error Correction Code (ECC) feature Memory...

...List Hotkey Del/F12 Function Enter BIOS Setup Utility/Enter Boot menu Description Press while the system is local configured L2 Cache RAM speed Full of the processor core clock frequency (Advanced Transfer Cache) L2 Cache function control Enable/Disable by BIOS Setup L2... The information below is only applicable to system installed with a Pentium 4 processor Tag RAM Location On Processor L2 Cache RAM Location On Processor L2 Cache RAM type PBSRAM (Pipelined-burst Synchronous RAM) L2 Cache RAM size Depends on CPU, which is booting to Error Correction Code (ECC) feature Memory...

Aspire L350 & Veriton 1000 Service Guide

Page 24

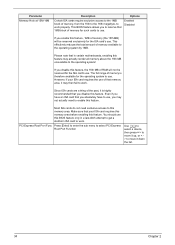

...-00D7FFF 00D8000-00DBFFF 00DC000-00DFFFF 00E0000-00E7FFF 00E8000-00EFFFF 00F0000-00FFFFF 0100000-0F9FFFF 0FA0000-0FFFFFF 1000000-FFFFFFF Size 640 KB System Memory 128 KB Video RAM 32 KB I/O Expansion ROM 16 KB I/O Expansion ROM 16 KB I/O Expansion ROM 16 KB I/O Expansion ROM 16 KB I/O Expansion ROM 32 KB for SCSI BIOS... for ROM on I/O Adapters Reserved for ROM on I/O Adapters Reserved for ROM on I/O Adapters Reserved for SCSI BIOS Reserved Onboard System ROM BIOS (ROM) System RAM BIOS (DRAM) Onboard DRAM Reserved for Memory Map I/O Card Non-Cacheable Onboard DRAM 16 Chapter 1

...-00D7FFF 00D8000-00DBFFF 00DC000-00DFFFF 00E0000-00E7FFF 00E8000-00EFFFF 00F0000-00FFFFF 0100000-0F9FFFF 0FA0000-0FFFFFF 1000000-FFFFFFF Size 640 KB System Memory 128 KB Video RAM 32 KB I/O Expansion ROM 16 KB I/O Expansion ROM 16 KB I/O Expansion ROM 16 KB I/O Expansion ROM 16 KB I/O Expansion ROM 32 KB for SCSI BIOS... for ROM on I/O Adapters Reserved for ROM on I/O Adapters Reserved for ROM on I/O Adapters Reserved for SCSI BIOS Reserved Onboard System ROM BIOS (ROM) System RAM BIOS (DRAM) Onboard DRAM Reserved for Memory Map I/O Card Non-Cacheable Onboard DRAM 16 Chapter 1

Aspire L350 & Veriton 1000 Service Guide

Page 33

N/A N/A Options Chapter 2 25 Parameter Base Memory Extended Memory Total Memory Description The amount of a particular computer. The base memory can usually be upgradable to a significantly higher amount. For example, a desktop machine with each model N/A of RAM that comes with 64MB might be upgraded to 768MB.

N/A N/A Options Chapter 2 25 Parameter Base Memory Extended Memory Total Memory Description The amount of a particular computer. The base memory can usually be upgradable to a significantly higher amount. For example, a desktop machine with each model N/A of RAM that comes with 64MB might be upgraded to 768MB.

Aspire L350 & Veriton 1000 Service Guide

Page 42

... ISA card to this feature. If you to use . Make sure that you enable this feature. Enabled Disabled If you disable this feature, 1MB of RAM will be reserved for such cards to reserve that 1MB block of the past, it down the list. 34 Chapter 2

... ISA card to this feature. If you to use . Make sure that you enable this feature. Enabled Disabled If you disable this feature, 1MB of RAM will be reserved for such cards to reserve that 1MB block of the past, it down the list. 34 Chapter 2

Aspire L350 & Veriton 1000 Service Guide

Page 87

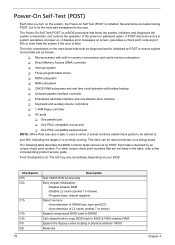

...in system operations at power-on, it displays error messages on the main board that are not listed in physical address 1000:0 Reserved 79 Chapter 4 Each task is initiated. Checkpoint CFh C0h C1h C3h C5h 01h 02h Description Test CMOS R/W functionality ... co-processor and cache memory subsystem T Direct Memory Access (DMA) controller T Interrupt system T Three programmable timers T ROM subsystem T RAM subsystem T CMOS RAM subsystem and real time clock/calendar with battery backup T Onboard parallel interface controller T Embedded hard disk interface and one diskette drive interface ...

...in system operations at power-on, it displays error messages on the main board that are not listed in physical address 1000:0 Reserved 79 Chapter 4 Each task is initiated. Checkpoint CFh C0h C1h C3h C5h 01h 02h Description Test CMOS R/W functionality ... co-processor and cache memory subsystem T Direct Memory Access (DMA) controller T Interrupt system T Three programmable timers T ROM subsystem T RAM subsystem T CMOS RAM subsystem and real time clock/calendar with battery backup T Onboard parallel interface controller T Embedded hard disk interface and one diskette drive interface ...