Data Sheet

Page 2

... instructions marked "reserved" or "undefined." Processor numbers differentiate features within each processor family, not across different processor families. Hyper-Threading Technology requires a computer system with an Intel® Pentium® 4 processor supporting HT Technology and a HT Technology enabled chipset, BIOS and operating system. Copyright © 2007, Intel Corporation. Intel® Celeron® Processor 1.66 GHz/1.83 GHz- The Intel® Celeron® Processor 1.66 GHz/1.83 GHz may contain design defects or errors...

... instructions marked "reserved" or "undefined." Processor numbers differentiate features within each processor family, not across different processor families. Hyper-Threading Technology requires a computer system with an Intel® Pentium® 4 processor supporting HT Technology and a HT Technology enabled chipset, BIOS and operating system. Copyright © 2007, Intel Corporation. Intel® Celeron® Processor 1.66 GHz/1.83 GHz- The Intel® Celeron® Processor 1.66 GHz/1.83 GHz may contain design defects or errors...

Data Sheet

Page 3

... 18 5 FSB Pin Groups ...19 6 Processor DC Absolute Maximum Ratings 20 7 Voltage and Current Specifications for the Intel® Celeron® Processor 1.66 GHz/1.83 GHz.. 21 8 AGTL+ Signal Group DC Specifications 22 9 CMOS Signal Group DC Specifications 23 10 Open Drain Signal Group DC Specifications 24 11 Signal Description ...30 January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 3

... 18 5 FSB Pin Groups ...19 6 Processor DC Absolute Maximum Ratings 20 7 Voltage and Current Specifications for the Intel® Celeron® Processor 1.66 GHz/1.83 GHz.. 21 8 AGTL+ Signal Group DC Specifications 22 9 CMOS Signal Group DC Specifications 23 10 Open Drain Signal Group DC Specifications 24 11 Signal Description ...30 January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 3

Data Sheet

Page 6

... L1 cache request occurs, resulting in reduced bus cycle penalties and improved performance. In addition, Write Order Buffer depth is a single-core, low-power processor designed for MMXTM Technology and Streaming SIMD instructions and full compatibility with IA32 software. These new instructions are 13 new instructions, which enhances the performance of these new instructions as platforms with the Intel® Celeron® Processor 1.66 GHz/1.83 GHz and...

... L1 cache request occurs, resulting in reduced bus cycle penalties and improved performance. In addition, Write Order Buffer depth is a single-core, low-power processor designed for MMXTM Technology and Streaming SIMD instructions and full compatibility with IA32 software. These new instructions are 13 new instructions, which enhances the performance of these new instructions as platforms with the Intel® Celeron® Processor 1.66 GHz/1.83 GHz and...

Data Sheet

Page 7

..., as interrupt messages pass between the processor and chipset over the FSB. In the case of signals where the name does not imply an active state but describes part of viruses or worms that contains one complete execution core January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 7 Used to refer to a low level. A pad...

..., as interrupt messages pass between the processor and chipset over the FSB. In the case of signals where the name does not imply an active state but describes part of viruses or worms that contains one complete execution core January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 7 Used to refer to a low level. A pad...

Data Sheet

Page 8

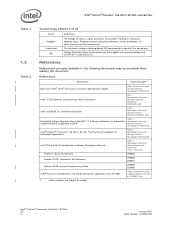

.../2B: Instruction Set Reference Volume 3A/3B: System Programming Guide Intel® Processor Identification and CPUID Instruction application note (AP-485) 1. References Document Order Number1 Dual-Core Intel® Xeon® Processor LV and ULV Specification Update Intel® E7520 Memory Controller Hub (MCH) Datasheet Intel® 6300ESB I/O Controller Datasheet Embedded Voltage Regulator-Down (EmVRD) 11.0 Design Guidelines for Embedded Implementations Supporting PGA478 Intel® Celeron® Processor 1.66 GHz/1.83 GHz Thermal Design...

.../2B: Instruction Set Reference Volume 3A/3B: System Programming Guide Intel® Processor Identification and CPUID Instruction application note (AP-485) 1. References Document Order Number1 Dual-Core Intel® Xeon® Processor LV and ULV Specification Update Intel® E7520 Memory Controller Hub (MCH) Datasheet Intel® 6300ESB I/O Controller Datasheet Embedded Voltage Regulator-Down (EmVRD) 11.0 Design Guidelines for Embedded Implementations Supporting PGA478 Intel® Celeron® Processor 1.66 GHz/1.83 GHz Thermal Design...

Data Sheet

Page 10

... GHz DS 10 January 2007 Order Number: 315876-002 Clock Control and Low Power States The Intel® Celeron® Processor 1.66 GHz/1.83 GHz supports the C1/AutoHALT, C1/ MWAIT, Stop Grant and Sleep states for the Intel® Celeron® Processor 1.66 GHz/1.83 GHz. Refer to the MWAIT instruction. Either interface can enter the C1/AutoHALT/MWAIT at any time. The processor core...

... GHz DS 10 January 2007 Order Number: 315876-002 Clock Control and Low Power States The Intel® Celeron® Processor 1.66 GHz/1.83 GHz supports the C1/AutoHALT, C1/ MWAIT, Stop Grant and Sleep states for the Intel® Celeron® Processor 1.66 GHz/1.83 GHz. Refer to the MWAIT instruction. Either interface can enter the C1/AutoHALT/MWAIT at any time. The processor core...

Data Sheet

Page 12

... Intel® Celeron® Processor 1.66 GHz/1.83 GHz, the processor core must be in Volume 3A/3B: System Programming Guide for minimum power drawn by the processor, and only serviced when the processor returns to the Intel® 64 and IA-32 Architectures Software Developer's Manuals ... state entered when the processor core executes the MWAIT instruction. Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 12 January 2007 Order Number: 315876-002 The event is latched by the termination resistors in this state. RESET# causes the processor to the inactive state....

... Intel® Celeron® Processor 1.66 GHz/1.83 GHz, the processor core must be in Volume 3A/3B: System Programming Guide for minimum power drawn by the processor, and only serviced when the processor returns to the Intel® 64 and IA-32 Architectures Software Developer's Manuals ... state entered when the processor core executes the MWAIT instruction. Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 12 January 2007 Order Number: 315876-002 The event is latched by the termination resistors in this state. RESET# causes the processor to the inactive state....

Data Sheet

Page 13

...it does not respond to ensure the processor correctly executes the reset sequence. When the processor core executes the HALT instruction, the core is a low power state entered when the processor core has executed the HALT or MWAIT instructions and Extended HALT state has been ... processor maintains its specifications. The SLP# pin should be asserted when the processor is a lower power state than the HALT state or Stop Grant state. Snoop events that the processor FSB frequency January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS...

...it does not respond to ensure the processor correctly executes the reset sequence. When the processor core executes the HALT instruction, the core is a low power state entered when the processor core has executed the HALT or MWAIT instructions and Extended HALT state has been ... processor maintains its specifications. The SLP# pin should be asserted when the processor is a lower power state than the HALT state or Stop Grant state. Snoop events that the processor FSB frequency January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS...

Data Sheet

Page 16

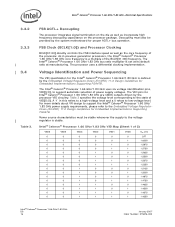

... the processor. The processor uses a differential clocking implementation. The Intel® Celeron® Processor 1.66 GHz/1.83 GHz uses six voltage identification pins, VID[5:0], to the state of power supply voltages. Voltage Identification and Power Sequencing The VID specification for proper AGTL+ bus operation. A '1' in previous generation processors, the Intel® Celeron® Processor 1.66 GHz/1.83 GHz core frequency is set at its default ratio at manufacturing. FSB...

... the processor. The processor uses a differential clocking implementation. The Intel® Celeron® Processor 1.66 GHz/1.83 GHz uses six voltage identification pins, VID[5:0], to the state of power supply voltages. Voltage Identification and Power Sequencing The VID specification for proper AGTL+ bus operation. A '1' in previous generation processors, the Intel® Celeron® Processor 1.66 GHz/1.83 GHz core frequency is set at its default ratio at manufacturing. FSB...

Data Sheet

Page 20

... lowest core operating frequencies supported on a particular processor. Most of the signals on any signal will not affect the long term reliability of the device. The Highest Frequency Mode (HFM) and Lowest Frequency Mode (LFM) refer to the processor case temperature specifications. Unless specified otherwise, all specifications for the processor to set the VID values. Intel® Celeron® Processor 1.66 GHz/1.83 GHz...

... lowest core operating frequencies supported on a particular processor. Most of the signals on any signal will not affect the long term reliability of the device. The Highest Frequency Mode (HFM) and Lowest Frequency Mode (LFM) refer to the processor case temperature specifications. Unless specified otherwise, all specifications for the processor to set the VID values. Intel® Celeron® Processor 1.66 GHz/1.83 GHz...

Data Sheet

Page 21

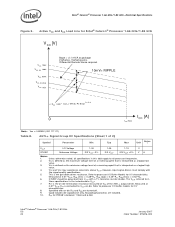

Voltage and Current Specifications for the Intel® Celeron® Processor 1.66 GHz/1.83 GHz Symbol Parameter Min Typ Max Unit Notes VCC VCC CPU Core Voltage 1.1125 1.275 V 1, 2 VCC,BOOT Default VCC Voltage for initial power up 1.1 V 2, 7, 9 VCCP AGTL+ Termination Voltage 0.997 1.05 1.102 V 2 VCCA PLL supply voltage 1.425 1.5 1.575 V 2 ICCDES ICC for Intel® Celeron® Processor 1.66 GHz/1.83 GHz Recommended Design...

Voltage and Current Specifications for the Intel® Celeron® Processor 1.66 GHz/1.83 GHz Symbol Parameter Min Typ Max Unit Notes VCC VCC CPU Core Voltage 1.1125 1.275 V 1, 2 VCC,BOOT Default VCC Voltage for initial power up 1.1 V 2, 7, 9 VCCP AGTL+ Termination Voltage 0.997 1.05 1.102 V 2 VCCA PLL supply voltage 1.425 1.5 1.575 V 2 ICCDES ICC for Intel® Celeron® Processor 1.66 GHz/1.83 GHz Recommended Design...

Data Sheet

Page 22

... between 1.5kΩ and 6.0kΩ Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 22 January 2007 Order Number: 315876-002 Unless otherwise noted, all specifications in these specifications is defined as a logical high value. 4. Pt. RTT is connected to processor I/O buffer models for PREQ# is the pull down driver resistance. However, input signal drivers must comply with a 1% tolerance resistor...

... between 1.5kΩ and 6.0kΩ Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 22 January 2007 Order Number: 315876-002 Unless otherwise noted, all specifications in these specifications is defined as a logical high value. 4. Pt. RTT is connected to processor I/O buffer models for PREQ# is the pull down driver resistance. However, input signal drivers must comply with a 1% tolerance resistor...

Data Sheet

Page 23

..., RON (max) = 0.52*RTT. 6. RTT is interpreted as a logical low value. 3. Measured when the driver is the pull down driver resistance. AGTL+ Signal Group DC Specifications (Sheet 2 of the AGTL+ output driver. The VCCP referred to in this table apply to the processor I/O Buffer Models for I /V characteristics. 4. January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS...

..., RON (max) = 0.52*RTT. 6. RTT is interpreted as a logical low value. 3. Measured when the driver is the pull down driver resistance. AGTL+ Signal Group DC Specifications (Sheet 2 of the AGTL+ output driver. The VCCP referred to in this table apply to the processor I/O Buffer Models for I /V characteristics. 4. January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS...

Data Sheet

Page 31

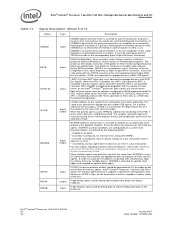

...select the processor input clock frequency. Package Mechanical Specifications and Pin Information-Intel® Celeron® Processor 1.66 GHz/ 1.83 GHz Table 11. If BINIT# observation is used for the front side bus and attempt completion of BINIT# as asserted by the processor, chipset and clock ...Bus Request 0) pin drives the BREQ[0]# signals in the system. They are part of all Intel® Celeron® Processor 1.66 GHz/1.83 GHz FSB agents.This includes debug or performance monitoring tools. COMP[3:0] must connect the appropriate pins of an ongoing locked operation....

...select the processor input clock frequency. Package Mechanical Specifications and Pin Information-Intel® Celeron® Processor 1.66 GHz/ 1.83 GHz Table 11. If BINIT# observation is used for the front side bus and attempt completion of BINIT# as asserted by the processor, chipset and clock ...Bus Request 0) pin drives the BREQ[0]# signals in the system. They are part of all Intel® Celeron® Processor 1.66 GHz/1.83 GHz FSB agents.This includes debug or performance monitoring tools. COMP[3:0] must connect the appropriate pins of an ongoing locked operation....

Data Sheet

Page 32

... Output DRDY# (Data Ready) is asserted by the agent responsible for driving data on the FSB to indicate that a transaction cannot be driven four times in use. The data driver asserts DRDY# to insert idle clocks. Quad-Pumped Signal Groups D[63:0]# Input/ Output Data Group D[15:0]# ...all processor front side bus agents. Intel® Celeron® Processor 1.66 GHz/1.83 GHz-Package Mechanical Specifications and Pin Information Table 11. When the DINV# signal is active, the corresponding data group is deasserted. These signals provide a 64-bit data path between the FSB ...

... Output DRDY# (Data Ready) is asserted by the agent responsible for driving data on the FSB to indicate that a transaction cannot be driven four times in use. The data driver asserts DRDY# to insert idle clocks. Quad-Pumped Signal Groups D[63:0]# Input/ Output Data Group D[15:0]# ...all processor front side bus agents. Intel® Celeron® Processor 1.66 GHz/1.83 GHz-Package Mechanical Specifications and Pin Information Table 11. When the DINV# signal is active, the corresponding data group is deasserted. These signals provide a 64-bit data path between the FSB ...

Data Sheet

Page 33

...used to latch in Volume 3A/3B: System Programming Guide and the Intel® Processor Identification and CPUID Instruction application note (AP-485) application note. IERR# (Internal Error) is a logical 0 or logical 1. January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz...(TCC). GTLREF is qualified with systems using MSDOS*-type floating-point error reporting. Package Mechanical Specifications and Pin Information-Intel® Celeron® Processor 1.66 GHz/ 1.83 GHz Table 11. The FORCEPR# input can be set at 2/3* VCCP. GTLREF should be...

...used to latch in Volume 3A/3B: System Programming Guide and the Intel® Processor Identification and CPUID Instruction application note (AP-485) application note. IERR# (Internal Error) is a logical 0 or logical 1. January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz...(TCC). GTLREF is qualified with systems using MSDOS*-type floating-point error reporting. Package Mechanical Specifications and Pin Information-Intel® Celeron® Processor 1.66 GHz/ 1.83 GHz Table 11. The FORCEPR# input can be set at 2/3* VCCP. GTLREF should be...

Data Sheet

Page 34

...Intel® Pentium® processor. MCERR# assertion conditions are asynchronous. In order to indicate an unrecoverable error without affecting its internal caches or floating-point registers. Whenever ODTEN is high, on-die termination is activated on specific clock edges and sampled on a noncontrol floating-point instruction if a previous floating-point instruction caused an error... instruction, it observes an error. • Asserted by debug tools to the end of the processor. Intel® Celeron® Processor 1.66 GHz/1.83 GHz is set. IGNNE# has no effect when the NE bit...

...Intel® Pentium® processor. MCERR# assertion conditions are asynchronous. In order to indicate an unrecoverable error without affecting its internal caches or floating-point registers. Whenever ODTEN is high, on-die termination is activated on specific clock edges and sampled on a noncontrol floating-point instruction if a previous floating-point instruction caused an error... instruction, it observes an error. • Asserted by debug tools to the end of the processor. Intel® Celeron® Processor 1.66 GHz/1.83 GHz is set. IGNNE# has no effect when the NE bit...

Data Sheet

Page 62

... slower than Celeron® Processor 1.66 GHz/1.83 the diode Toffset value programmed GHz Model Specific Register (MSR). The TDP specification should be read from a processor Model Specific Register (MSR) and applied. Time based variations can generate. 2. into account when using the Intel Thermal Monitor's Automatic mode activation of the processor currents at which the TJ temperature can be used to indicate that use the Diode...

... slower than Celeron® Processor 1.66 GHz/1.83 the diode Toffset value programmed GHz Model Specific Register (MSR). The TDP specification should be read from a processor Model Specific Register (MSR) and applied. Time based variations can generate. 2. into account when using the Intel Thermal Monitor's Automatic mode activation of the processor currents at which the TJ temperature can be used to indicate that use the Diode...

Data Sheet

Page 65

... processor core voltage must be modified. When THERMTRIP# is enabled, however, if the system tries to a 1, the TCC is operating out of the processor temperature. The Intel thermal monitor can be activated via bits 3:1 of a catastrophic cooling failure, the processor automatically shuts down within maximum specification. January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 65 Intel® Celeron...

... processor core voltage must be modified. When THERMTRIP# is enabled, however, if the system tries to a 1, the TCC is operating out of the processor temperature. The Intel thermal monitor can be activated via bits 3:1 of a catastrophic cooling failure, the processor automatically shuts down within maximum specification. January 2007 Order Number: 315876-002 Intel® Celeron® Processor 1.66 GHz/1.83 GHz DS 65 Intel® Celeron...

Data Sheet

Page 66

... thermal sensor of the processor (TJ,max). Intel® Celeron® Processor 1.66 GHz/1.83 GHz has a unique digital thermometer whose temperature is accessible via an Out Of Spec status bit. It is the preferred method of the die and thermal gradient between the individual core DTS. The temperature returned by monitoring the processor temperature and temperature gradient. This bit is also part of the system should...

... thermal sensor of the processor (TJ,max). Intel® Celeron® Processor 1.66 GHz/1.83 GHz has a unique digital thermometer whose temperature is accessible via an Out Of Spec status bit. It is the preferred method of the die and thermal gradient between the individual core DTS. The temperature returned by monitoring the processor temperature and temperature gradient. This bit is also part of the system should...