Data Sheet

Page 22

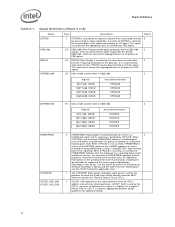

... Source Synchronous I /O group when receiving. BPM4#, BPM[2:1]#, BPMb[2:1]# ADS#, AP[1:0]#, BINIT#2, BNR#2, BPM5#, BPM3#, BPM0#,BPMb3#, BPMb0#, BR[1:0]#, DBSY#, DP[3:0]#, DRDY#, HIT#2, HITM#2, LOCK#, MCERR#2 Signals Associated Strobe REQ[4:0]#,A[16:3]#, ADSTB0# A[37:36]# A[35:17]# D[15:0]#, DBI0# D[31:16]#, DBI1...combined into groups by buffer type. FSB Signal Groups (Sheet 1 of BCLK0. Similarly, "AGTL+ Output" refers to assoc. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications The TESTHI signals must be used for each signal: • TESTHI10 - In this ...

... Source Synchronous I /O group when receiving. BPM4#, BPM[2:1]#, BPMb[2:1]# ADS#, AP[1:0]#, BINIT#2, BNR#2, BPM5#, BPM3#, BPM0#,BPMb3#, BPMb0#, BR[1:0]#, DBSY#, DP[3:0]#, DRDY#, HIT#2, HITM#2, LOCK#, MCERR#2 Signals Associated Strobe REQ[4:0]#,A[16:3]#, ADSTB0# A[37:36]# A[35:17]# D[15:0]#, DBI0# D[31:16]#, DBI1...combined into groups by buffer type. FSB Signal Groups (Sheet 1 of BCLK0. Similarly, "AGTL+ Output" refers to assoc. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications The TESTHI signals must be used for each signal: • TESTHI10 - In this ...

Data Sheet

Page 23

Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications Table 2-6. Table 2-9. These signals may be driven simultaneously by multiple agents (Wired-OR). Table...VSS_DIE_SENSE, VSS_DIE_SENSE2, VTT_SEL Notes: 1. Signal Reference Voltages GTLREF CMOS A[37:3]#, ADS#, ADSTB[1:0]#, AP[1:0]#, BINIT#, BNR#, BPM[5:0]#, BPMb[3:0]#, BPRI#, BR[1:0]#, D[63:0]#, DBI[3:0]#, DBSY#, DEFER#, DP[3:0]#, DRDY#, DSTBN[3:0]#, DSTBP[3:0]#, FORCEPR#, HIT#, HITM#, LOCK#, MCERR#, RESET#, REQ[4:0]#, RS[2:0]#, RSP#, TRDY# A20M#, LINT0/INTR, LINT1/NMI, IGNNE#, INIT#, PWRGOOD, SMI#, STPCLK...

Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications Table 2-6. Table 2-9. These signals may be driven simultaneously by multiple agents (Wired-OR). Table...VSS_DIE_SENSE, VSS_DIE_SENSE2, VTT_SEL Notes: 1. Signal Reference Voltages GTLREF CMOS A[37:3]#, ADS#, ADSTB[1:0]#, AP[1:0]#, BINIT#, BNR#, BPM[5:0]#, BPMb[3:0]#, BPRI#, BR[1:0]#, D[63:0]#, DBI[3:0]#, DBSY#, DEFER#, DP[3:0]#, DRDY#, DSTBN[3:0]#, DSTBP[3:0]#, FORCEPR#, HIT#, HITM#, LOCK#, MCERR#, RESET#, REQ[4:0]#, RS[2:0]#, RSP#, TRDY# A20M#, LINT0/INTR, LINT1/NMI, IGNNE#, INIT#, PWRGOOD, SMI#, STPCLK...

Data Sheet

Page 74

... Ready) is asserted by STPCLK#. I The FORCEPR# (force power reduction) input can be used by the platform to cause the Quad-Core Intel® Xeon® Processor 5400 Series to determine if a signal is used by the AGTL+ receivers to activate the Thermal Control Circuit (TCC)....DSTBN3# DSTBP[3:0]# I DEFER# is qualified by the data driver on each data 3 transfer, indicating valid data on the data bus. I /O DP[3:0]# (Data Parity) provide parity protection for AGTL+ address and common clock input lands. I GTLREF_ADD determines the signal reference level for the D[63...

... Ready) is asserted by STPCLK#. I The FORCEPR# (force power reduction) input can be used by the platform to cause the Quad-Core Intel® Xeon® Processor 5400 Series to determine if a signal is used by the AGTL+ receivers to activate the Thermal Control Circuit (TCC)....DSTBN3# DSTBP[3:0]# I DEFER# is qualified by the data driver on each data 3 transfer, indicating valid data on the data bus. I /O DP[3:0]# (Data Parity) provide parity protection for AGTL+ address and common clock input lands. I GTLREF_ADD determines the signal reference level for the D[63...