Data Sheet

Page 9

...of the 64-bit extension technology. Intel® Thermal Monitor 1 and Intel® Thermal Monitor provide efficient and effective cooling in the Intel® 64 and IA-32 Architectures Software Developer's Manual, at http://www.intel.com/cd/ids/developer/asmona/eng... environments. The Quad-Core Intel® Xeon® Processor 5400 Series support Intel® Virtualization Technology for data movement. The Quad-Core Intel® Xeon® Processor 5400 Series support Intel® 64 Architecture as executable or non executable. In addition, the Quad-Core Intel® Xeon® Processor ...

...of the 64-bit extension technology. Intel® Thermal Monitor 1 and Intel® Thermal Monitor provide efficient and effective cooling in the Intel® 64 and IA-32 Architectures Software Developer's Manual, at http://www.intel.com/cd/ids/developer/asmona/eng... environments. The Quad-Core Intel® Xeon® Processor 5400 Series support Intel® Virtualization Technology for data movement. The Quad-Core Intel® Xeon® Processor 5400 Series support Intel® 64 Architecture as executable or non executable. In addition, the Quad-Core Intel® Xeon® Processor ...

Data Sheet

Page 13

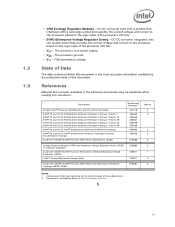

...'s Manual Documentation Changes Quad-Core Intel® Xeon® Processor 5400 Series Specification Update Document Number1 241618 253665 253666 253667 253668 253669 248966 252046 318585 Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.0 Design Guidelines Quad-Core Intel® Xeon® Processor 5400 Series Thermal/Mechanical Design Guidelines (TMDG) LGA771 Socket Mechanical Design Guide 315889 318611 313871 Quad-Core Intel...

...'s Manual Documentation Changes Quad-Core Intel® Xeon® Processor 5400 Series Specification Update Document Number1 241618 253665 253666 253667 253668 253669 248966 252046 318585 Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.0 Design Guidelines Quad-Core Intel® Xeon® Processor 5400 Series Thermal/Mechanical Design Guidelines (TMDG) LGA771 Socket Mechanical Design Guide 315889 318611 313871 Quad-Core Intel...

Data Sheet

Page 17

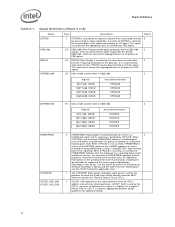

... ratio can operate. The lowest bus ratio supported by the Quad-Core Intel® Xeon® Processor 5400 Series is configured during manufacturing. The processor core frequency is 1/6. 2.4.1 Front Side Bus Frequency Select Signals (...Quad-Core Intel® Xeon® Processor 5400 Series core frequency is set to the Intel® 64 and Intel® 64 and IA-32 Architectures Software Developer's Manual. The processor bus ratio multiplier is a multiple of the processor. BSEL[2:0] are used to FSB multipliers and their corresponding core frequencies. Quad-Core Intel® Xeon...

... ratio can operate. The lowest bus ratio supported by the Quad-Core Intel® Xeon® Processor 5400 Series is configured during manufacturing. The processor core frequency is 1/6. 2.4.1 Front Side Bus Frequency Select Signals (...Quad-Core Intel® Xeon® Processor 5400 Series core frequency is set to the Intel® 64 and Intel® 64 and IA-32 Architectures Software Developer's Manual. The processor bus ratio multiplier is a multiple of the processor. BSEL[2:0] are used to FSB multipliers and their corresponding core frequencies. Quad-Core Intel® Xeon...

Data Sheet

Page 74

...and must connect the appropriate pins of all processor FSB agents. Signal Definitions (Sheet 4 of the Intel® 64 and IA-32 Architectures Software Developer's Manual and the Intel Processor Identification and the CPUID Instruction application note. They are driven by the data driver on each ... and its meaning is qualified by the AGTL+ receivers to determine if a signal is asserted by the platform to cause the Quad-Core Intel® Xeon® Processor 5400 Series to the Normal state. When STPCLK# is asserted, an assertion of all processor FSB agents. This signal...

...and must connect the appropriate pins of all processor FSB agents. Signal Definitions (Sheet 4 of the Intel® 64 and IA-32 Architectures Software Developer's Manual and the Intel Processor Identification and the CPUID Instruction application note. They are driven by the data driver on each ... and its meaning is qualified by the AGTL+ receivers to determine if a signal is asserted by the platform to cause the Quad-Core Intel® Xeon® Processor 5400 Series to the Normal state. When STPCLK# is asserted, an assertion of all processor FSB agents. This signal...

Data Sheet

Page 76

... all FSB agents will remain active until they come within two clocks. These signals are configurable at the active-to the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3. This indicates that the processor has reached its maximum safe operating temperature. The processor requires this 2 signal to ADSTB[1:0]#. This...

... all FSB agents will remain active until they come within two clocks. These signals are configurable at the active-to the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3. This indicates that the processor has reached its maximum safe operating temperature. The processor requires this 2 signal to ADSTB[1:0]#. This...

Data Sheet

Page 91

... the TCC goes inactive and clock modulation ceases. Intel® Thermal Monitor 2 The Quad-Core Intel® Xeon® Processor 5400 Series adds supports for both processor cores. Not all Quad-Core Intel® Xeon® Processor 5400 Series are capable of reduced ...due to the Quad-Core Intel® Xeon® Processor X5482, Quad-Core Intel® Xeon® Processor X5400 Series, and Quad-Core Intel® Xeon® Processor E5400 Series, and Quad-Core Intel® Xeon® Processor L5400 Series Thermal Profile, it would only be activated for Intel® Thermal Monitor...

... the TCC goes inactive and clock modulation ceases. Intel® Thermal Monitor 2 The Quad-Core Intel® Xeon® Processor 5400 Series adds supports for both processor cores. Not all Quad-Core Intel® Xeon® Processor 5400 Series are capable of reduced ...due to the Quad-Core Intel® Xeon® Processor X5482, Quad-Core Intel® Xeon® Processor X5400 Series, and Quad-Core Intel® Xeon® Processor E5400 Series, and Quad-Core Intel® Xeon® Processor L5400 Series Thermal Profile, it would only be activated for Intel® Thermal Monitor...

Data Sheet

Page 93

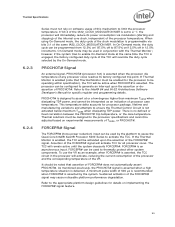

...temperature. This temperature delta accounts for processor package, lifetime and manufacturing variations and attempts to the Intel® 64 and IA-32 Architectures Software Developer's Manual for the processor to be operating within specification), the TCC will immediately reduce its factory configured trip...below maximum TCASE when dissipating TDP power. The TCC will override the duty cycle selected by the platform to cause the Quad-Core Intel® Xeon® Processor 5400 Series to activate the TCC. As mentioned previously, the PROCHOT# signal is asserted when a high ...

...temperature. This temperature delta accounts for processor package, lifetime and manufacturing variations and attempts to the Intel® 64 and IA-32 Architectures Software Developer's Manual for the processor to be operating within specification), the TCC will immediately reduce its factory configured trip...below maximum TCASE when dissipating TDP power. The TCC will override the duty cycle selected by the platform to cause the Quad-Core Intel® Xeon® Processor 5400 Series to activate the TCC. As mentioned previously, the PROCHOT# signal is asserted when a high ...

Data Sheet

Page 98

... support for the processor to remain within its specifications. When one of the processor cores execute the HALT or MWAIT instruction, that processor core is enabled via the BIOS. See the Intel® 64 and IA-32 Architecture Software Developer's Manual. The system can be enabled for the processor. Extended HALT State Extended HALT...

... support for the processor to remain within its specifications. When one of the processor cores execute the HALT or MWAIT instruction, that processor core is enabled via the BIOS. See the Intel® 64 and IA-32 Architecture Software Developer's Manual. The system can be enabled for the processor. Extended HALT State Extended HALT...

Data Sheet

Page 101

... Architectures Software Developer's Manual. After the snoop is serviced or the interrupt is software controlled. After the snoop is serviced or the interrupt is not enabled in HALT state. Not all Quad-Core Intel® Xeon® Processor 5400 Series are handled the same way as appropriate. Enhanced Intel SpeedStep® Technology Quad-Core Intel® Xeon® Processor 5400...

... Architectures Software Developer's Manual. After the snoop is serviced or the interrupt is software controlled. After the snoop is serviced or the interrupt is not enabled in HALT state. Not all Quad-Core Intel® Xeon® Processor 5400 Series are handled the same way as appropriate. Enhanced Intel SpeedStep® Technology Quad-Core Intel® Xeon® Processor 5400...

Data Sheet

Page 115

...shipped with an external ambient temperature of 35°C. They are required to complete this solution will include the following items: • Quad-Core Intel® Xeon® Processor 5400 Series • Unattached heat sink solution • Four screws, four springs, and four heat sink standoffs (... is due to the requirement of additional space at or below 5°C based on heat sink) • Installation and warranty manual • Intel Inside Logo Other items listed in order to both copper and aluminum heatsink solutions. These specifications apply to avoid damage. This is...

...shipped with an external ambient temperature of 35°C. They are required to complete this solution will include the following items: • Quad-Core Intel® Xeon® Processor 5400 Series • Unattached heat sink solution • Four screws, four springs, and four heat sink standoffs (... is due to the requirement of additional space at or below 5°C based on heat sink) • Installation and warranty manual • Intel Inside Logo Other items listed in order to both copper and aluminum heatsink solutions. These specifications apply to avoid damage. This is...