Technical Product Specification

Page 23

...1q • TCP, IP, and UDP checksum offload (for IPv4 and IPv6) • Full device driver compatibility 1.11.2 LAN Subsystem Software LAN software and drivers are available from Intel's World Wide Web site. Product Description 1.11 LAN Subsystem The LAN subsystem consists of the LAN subsystem ...include: • CSMA/CD protocol engine • LAN connect interface between the Integrated LAN Controller and the Physical Layer (PHY): PCI ...

...1q • TCP, IP, and UDP checksum offload (for IPv4 and IPv6) • Full device driver compatibility 1.11.2 LAN Subsystem Software LAN software and drivers are available from Intel's World Wide Web site. Product Description 1.11 LAN Subsystem The LAN subsystem consists of the LAN subsystem ...include: • CSMA/CD protocol engine • LAN connect interface between the Integrated LAN Controller and the Physical Layer (PHY): PCI ...

Technical Product Specification

Page 28

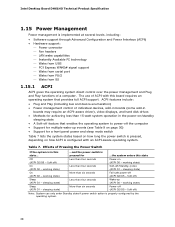

... system that provides full ACPI support. Intel Desktop Board DH61HO Technical Product Specification 1.15 Power Management... Power management is implemented at several levels, including: • Software support through Advanced Configuration and Power Interface (ACPI) • Hardware support: Power connector Fan headers LAN wake capabilities Instantly Available PC technology Wake from USB PCI...is in boards may require an ACPI-aware driver), video displays, and hard disk drives &#...

... system that provides full ACPI support. Intel Desktop Board DH61HO Technical Product Specification 1.15 Power Management... Power management is implemented at several levels, including: • Software support through Advanced Configuration and Power Interface (ACPI) • Hardware support: Power connector Fan headers LAN wake capabilities Instantly Available PC technology Wake from USB PCI...is in boards may require an ACPI-aware driver), video displays, and hard disk drives &#...

Technical Product Specification

Page 33

...use of providing adequate +5 V standby current. Add-in boards that supports Wake from an ACPI S3 state. The board supports the PCI Bus Power Management Interface Specification. Failure to provide adequate standby current when implementing Instantly Available PC technology can be used to wake the ...-state. NOTE Wake from USB requires the use of Instantly Available PC technology requires operating system support and PCI 2.2 compliant add-in cards, PCI Express add-in cards, and drivers. 1.15.2.5 Wake from USB USB bus activity wakes the computer from USB and is supported by the ...

...use of providing adequate +5 V standby current. Add-in boards that supports Wake from an ACPI S3 state. The board supports the PCI Bus Power Management Interface Specification. Failure to provide adequate standby current when implementing Instantly Available PC technology can be used to wake the ...-state. NOTE Wake from USB requires the use of Instantly Available PC technology requires operating system support and PCI 2.2 compliant add-in cards, PCI Express add-in cards, and drivers. 1.15.2.5 Wake from USB USB bus activity wakes the computer from USB and is supported by the ...

Technical Product Specification

Page 63

...- 0x5F 0x60 - 0x6F 0x70 - 0x7F 0x80 - 0x8F 0x90 - 0x9F 0xA0 - 0xAF 0xB0 - 0xBF 0xC0 - 0xCF 0xD0 - 0xDF 0xF0 - 0xFF Entering SX states S0 to I /O buses: PCI, USB, ATA, etc. 0x5F is useful for determining the point where an error occurred. Resuming from SX states. 0x10 -0x20 - Start with... Input devices: Keyboard/Mouse. S3, etc. Security (SEC) phase PEI phase pre MRC execution MRC memory detection PEI phase post MRC execution Recovery Platform DXE driver CPU Initialization (PEI, DXE, SMM) I /O port 80h. If the POST fails, execution stops and the last POST code generated is left at this point...

...- 0x5F 0x60 - 0x6F 0x70 - 0x7F 0x80 - 0x8F 0x90 - 0x9F 0xA0 - 0xAF 0xB0 - 0xBF 0xC0 - 0xCF 0xD0 - 0xDF 0xF0 - 0xFF Entering SX states S0 to I /O buses: PCI, USB, ATA, etc. 0x5F is useful for determining the point where an error occurred. Resuming from SX states. 0x10 -0x20 - Start with... Input devices: Keyboard/Mouse. S3, etc. Security (SEC) phase PEI phase pre MRC execution MRC memory detection PEI phase post MRC execution Recovery Platform DXE driver CPU Initialization (PEI, DXE, SMM) I /O port 80h. If the POST fails, execution stops and the last POST code generated is left at this point...